Haltung bewahren in der Mikrowelt

Neuartige elektrostatische Träger für ultradünne Wafer eröffnen neue Möglichkeiten beim Design von verlustarmen Leistungselektronik-Bausteinen oder 3D-integrierten Chip-Aufbauten.

Neuartige elektrostatische Träger für ultradünne Wafer eröffnen neue Möglichkeiten beim Design von verlustarmen Leistungselektronik-Bausteinen oder 3D-integrierten Chip-Aufbauten.

Mikrochips werden klassischerweise auf Silizium-Scheiben – den Wafern – prozessiert. Doch für einige Anwendungen sind die Wafer mittlerweile so dünn, dass Ihre Handhabung für viele Firmen zum Problem wird. Eine elegante Lösung für die Herstellung extrem dünner mikroelektronischer Komponenten, die Realisierung von verlustarmen Leistungselektronik-Bausteinen oder die Entwicklung von 3D-integrierten Chip-Aufbauten hat nun das Fraunhofer IZM entwickelt.

Die Technik ist deshalb besonders interessant, weil durch sie auch dünnste Wafer im Dickenbereich von 20–50 µm in den vorhandenen Prozessanlagen der Halbleiterindustrie weiterprozessiert werden können. Dazu werden die gedünnten bzw. die zu dünnenden Produkt-Wafer auf einen spezifisch präparierten Träger-Wafer gelegt und anschließend durch Aufladen einer großflächigen Elektrodenstruktur elektrostatisch fixiert.

Es hat sich gezeigt, dass bei Auswahl einer geeigneten dielektrischen Beschichtung auf dem Träger-Substrat eine lang andauernde elektrische Polarisierung erzielt wird. Der dünne Wafer bleibt somit auch nach Abkopplung der Ladespannung sicher auf dem Träger fixiert und kann weitere Prozessschritte durchlaufen. Nach Beendigung der Fertigungssequenz wird die Elektrodenstruktur entladen, und der gedünnte Wafer kann leicht wieder entfernt werden.

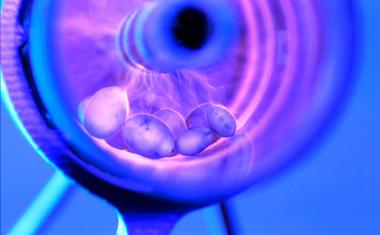

Abb.: Träger im Ofen. Die elektrostatische Haltekraft ist auch bei Temperaturen über 400 °C noch aktiv. (Quelle: Fraunhofer IZM)

Da für diese neue Trägertechnik keine polymeren Klebstoffe benötigt werden, sind nach dem Ablösen des zu bearbeitenden Wafers auch keine Reinigungsprozeduren erforderlich.

Das Trägersubstrat selbst ist ein Silizium-Wafer, der in Dünnfilmtechnik strukturiert und an der Kontaktfläche zum fixierten dünnen Wafer vollständig elektrisch isoliert ist. Die Kontaktstellen zum Aufladen der Elektroden können an der Vorder- oder Rückseite des Trägersubstrats realisiert werden.

Im Gegensatz zu anderen Trägermaterialien, wie z. B. Glas, Saphir oder Keramik, bietet Silizium die entscheidenden Vorteile einer sehr guten Wärmeleitfähigkeit und, im Falle der Handhabung von dünnen Silizium-Wafern, auch einen ideal angepassten Wärmeausdehnungskoeffizient.

Die elektrostatische Haltekraft ist auch bei Temperaturen über 400 °C noch aktiv. Somit bietet diese Trägertechnik erstmals die Möglichkeit, Prozessschritte an sehr dünnen Wafern bei hohen Temperaturen auszuführen. Beispiele hierfür sind das Legieren von Rückseitenmetallisierungen oder das Aufbringen und Plasma-Ätzen von dielektrischen Schichten.

Potenzielle Anwendungsgebiete der elektrostatischen Trägertechnik sind neben der Leistungselektronik auch opto-elektronische Produkte, Bumping-Prozesse an dünnen Wafern, die Herstellung noch dünnerer Solarzellensubstrate und viele weitere Technologiefelder, bei denen fragile Substrate prozessiert werden sollen.

Quelle: Fraunhofer IZM

Weitere Infos:

- Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM:

http://www.izm.fraunhofer.de - Waferpräparation:

http://www.izm-m.fhg.de/.../dieabteilungen3_n400407abteilungen_a_3.html