Geschrumpfter SRAM-Speicher

Physik Journal - Wissenschaftlern von IBM gelang es, eine SRAM-Zelle mit sechs Transistoren auf ein Zehntel der heute üblichen Größe schrumpfen zu lassen.

Physik Journal - Wissenschaftlern von IBM gelang es, eine SRAM-Zelle mit sechs Transistoren auf ein Zehntel der heute üblichen Größe schrumpfen zu lassen.

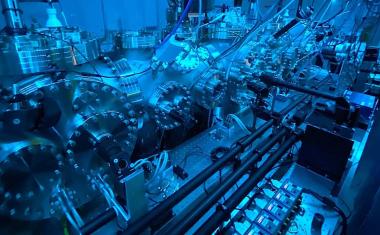

Schnelle Zugriffszeiten und hohe Taktfrequenzen verlangen im Computer nach sehr schnellen, flüchtigen Arbeitsspeichern. Diese Aufgabe erfüllen SRAM-Module (Static Random Access Memory), die im Unterschied zu den langsameren DRAM-Speichern (Dynamic Random Access Memory) allerdings mehr Platz benötigen und aufwändiger zu produzieren sind. Doch Wissenschaftlern vom IBM-Forschungslabor in Yorktown Heights gelang es nun, eine SRAM-Zelle mit sechs Transistoren auf ein Zehntel der heute üblichen Größe schrumpfen zu lassen. Auf dem IEDM-Treffen (International Electron Devices Meeting) in San Francisco präsentierten sie ihren nur 0,197 Quadratmikrometer kleinen Prototyp.

Der Schlüssel zu diesem Erfolg lag in der Kombination zweier Lithographie-Methoden, um Nanometer feine Strukturen in das Silizium zu bannen. Für die gröberen Abschnitte bis etwa 150 Nanometer Größe nutzten sie klassisch die Photolithographie (Wellenlänge des Belichtungslichts: 248 Nanometer). Doch für eine möglichst exakte und symmetrische Dotierung des Gate-Polysiliziums sind Genauigkeiten von etwa zehn Nanometer nötig. Diese werden mit der Elektronenstrahl-Lithographie erreicht, mit der direkt auf dem Chip eine Art Schablone für den Ionenstrahl des Dotierungsmaterials erzeugt wird. Auf 5 bis 50 Kilovolt beschleunigte Elektronen „belichten“ dazu einen Fotolack (Polymethylmethacrylat). Die unbelichteten Bereiche bleiben bei der Entwicklung erhalten, sodass eine exakt durchlöcherte Maske für die darauf folgende Implantation der Ionen entsteht. Die Dotier-Ionen treffen beim Flug durch diese Maske auf wenige Nanometer genau nur an den gewünschten Stellen auf das Polysilizium und lagern sich in das Material ein.

Mit dieser Technik greifen die IBM-Forscher der „ITRS-Roadmap“, der Planungsgrundlage der Chiphersteller, schon um Jahre voraus. Denn erst Anfang des kommenden Jahrzehnts wird mit Fertigungstechniken für 45 oder gar 32 Nanometer feine Chipstrukturen gerechnet. Bis die Kombination aus ausgereifter Photolithographie und aufwändiger Elektronenstrahl-Lithographie in den Chipfabriken einzieht, können jedoch noch vier bis fünf Jahre vergehen. Im Prinzip aber halten es die IBM-Experten für möglich, noch feinere Strukturen von unter zehn Nanometern mit der Belichtung über Elektronen zu erzeugen.

Jan Oliver Löfken

Quelle: Physik Journal, Januar 2005