Stempeltechnik für schnellere Chips

Hauchdünne Streifen aus Verbindungshalbleitern lassen sich elegant mit Silizium-Technologie kombinieren.

Hauchdünne Streifen aus Verbindungshalbleitern lassen sich elegant mit Silizium-Technologie kombinieren.

Gemäß dem empirischen Gesetz von Moore verdoppelt sich die Rechenleistung von Prozessoren alle 12 bis 18 Monate. Doch diese rasante Entwicklung lässt sich allein mit dem Halbleiter Silizium bald nicht mehr aufrecht erhalten, da mit schrumpfenden Schaltkreisen störende Leckströme und Quanteneffekte zunehmen. Mit Hochdruck wird daher an neuen Werkstoffen geforscht, mit denen die Chipindustrie weiterhin die gewohnten Leistungssteigerungen erreichen könnten. Kalifornische Wissenschaftler fanden nun ein elegantes Druckverfahren, mit dem sie III-V-Verbindungshalbleiter wie Indiumarsenid in winzigen Streifen auf Silizium-Rohlinge drucken können.

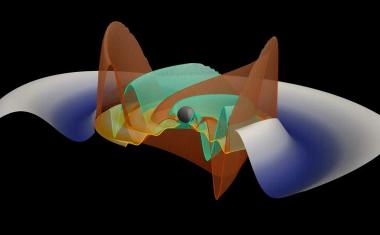

Abb.: Mikroskopaufnahme des "XOI"-Transistors mit Teilvergrößerung der "gedruckten" Indiumarsenid-Streifen (Bild: Ali Javey, University of California, Berkeley)

Diese Materialien zeichnen sich vor allem durch eine höhere Elektronenbeweglichkeit aus, die zu schnelleren Schaltprozessen führen können. Allerdings müssen die Werkstoffe dazu möglichst defektfrei in winzige Transistoren integriert werden können. Genau dieses Ziel verfolgen Ali Javey und seine Kollegen von der University of California in Berkeley mit einem Stempel-Druck-Verfahren. "Ultradünne Schichten aus Verbindungshalbleitern direkt auf Silizium-Trägern zeigen exzellente elektronische Eigenschaften", berichten die Forscher.

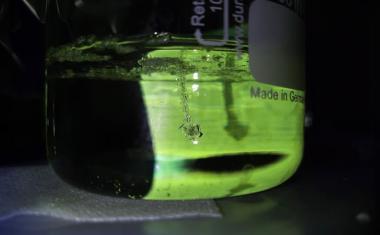

In einem ersten Schritt ließen die Forscher 15 bis 48 Nanometer dünne Streifen aus Indiumarsenid auf einer Galliumantimon-Unterlage wachsen. Darauf hoben sie die filigranen Streifen mit einem flexiblen Stempel aus Kunststoff, an den die Nanostreifen hafteten, ab und pressten diese auf einen konventionellen Träger aus Silizium und Siliziumdioxid. Dazwischen gewährleistete eine nur einen Nanometer dünne Schicht aus Indiumarsenoxiden eine ausreichende Isolation. Diese Halbleiter-Schichten deckten die Wissenschaftler darauf mit dünnen Lagen aus Zirkoniumoxid und Nickel ab.

Diese Komposite konnten mit den etablierten Methoden der Lithographie zu defektfreien Schaltkreisen strukturiert werden. Diese zeigten bei Schaltspannungen von 0,5 Volt herausragende Schalteigenschaften mit einem An-Aus-Stromverhältnis von mehr als 1 zu 10.000. Javey und Kollegen sind überzeugt, dass ihre Methode sich nicht nur für Indiumarsenid eignet, sondern auch auf andere III-V-Verbindungshalbleiter übertragen werden kann. Analog zu der etablierten Silicon-on-Insulator – kurz SOI – Technologie tauften sie ihr Verfahren auf XOI, wobei X stellvertretend für die genutzten Verbindungshalbleiter steht.

"Die Transistor-Eigenschaften sind sehr vielversprechend und die Elektronenbeweglichkeit stellt die von Silizium-Modulen weit in den Schatten", beurteilt John Rogers von der University of Illinois in einem begleitenden Kommentar die Ergebnisse seiner kalifornischen Kollegen. Wegen der großen Dynamik in der Chip-Industrie könnte dieses Stempel-Druck-Verfahren schon in wenigen Jahren zum Bau von neuen und deutlich leistungsfähigeren Prozessoren führen.

Jan Oliver Löfken

Weitere Infos

Weiterführende Literatur:

- Chau, R., Doyle, B., Datta, S., Kavalieros, J. & Zhang, K.: Nature Mater. 6, 810–812 (2007)

- Ko, H. C. et al.: Nature 454, 748–753 (2008)

- Kim, S. et al.: Proc. Natl. Acad. Sci. USA 107, 17095–17100 (2010)

- Yoon, J. et al.: Nature 465, 329–333 (2010)

AL