Programmierbarer Chip aus Nanodrähten

Forscher von der Harvard Universität bringen die Nanoelektronik voran.

Forscher von der Harvard Universität bringen die Nanoelektronik voran.

Die fortschreitende Miniaturisierung der Halbleiterelektronik mit lithographischen Methoden stößt zunehmend auf Probleme. Sind die Abmessungen der gefertigten Strukturen wesentlich kleiner als 100 Nanometer, so machen sich Schwankungen der Größe und der atomaren Zusammensetzung störend bemerkbar. Die elektronischen Bauelemente haben dann zu stark streuende Schlüsselparameter, so dass sie in integrierten Schaltungen Fehler verursachen können. Eine Alternative bieten kontrolliert gewachsene Nanodrähte, deren Querschnitt sich fast mit atomarer Präzision reproduzieren lässt. Jetzt wurden aus solchen Nanodrähten programmierbare Feldeffekttransistoren hergestellt und diese zu einem Nanoprozessor verschaltet.

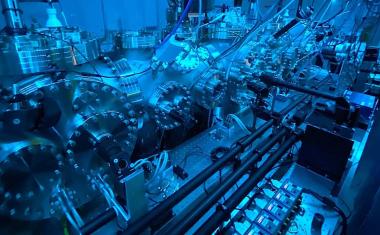

Abb.: Rasterelektronenmikroskopische Aufnahme des programmierbaren Nanodrahtprozessors. (Bild: Lieber Group, Harvard University)

Charles Lieber und seine Kollegen von der Harvard University und der MITRE Corporation haben zunächst 10 nm dicke Germanium-Nanodrähte hergestellt und mit einem 2 nm dicken Mantel aus Silizium versehen. Dazu haben sie Goldnanoteilchen als Katalysatoren auf eine oxidierte Siliziumunterlage gesetzt und diese in einem Ofen mit der Germaniumverbindung GeH4 bedampft. Nachdem unter den Goldteilchen Germaniumsäulen in die Höhe gewachsen waren, bekamen diese durch Bedampfung mit Monosilan (SiH4) einen Siliziummantel. Mit einem Stempelverfahren wurden die Nanoröhren auf eine strukturierte Oberfläche gebracht und ausgerichtet, so dass Bündel von parallel nebeneinander liegenden Röhren entstanden.

Aus jeder einzelnen Nanoröhre wurde ein winziger Feldeffekttransistor hergestellt. Dazu wurden die beiden Enden einer Röhre durch Elektronenstrahllithographie mit einer Source- und einer Drain-Elektrode versehen. Dann bekam die Röhre auf ihrer Oberseite eine Beschichtung, die elektrische Ladungen speichern konnte. Sie bestand aus einer elektrisch leitenden Zirkonoxidschicht, die von isolierenden Aluminiumoxidschichten umschlossen wurde. Schließlich wurden quer über das ganze Röhrenbündel mehrere linienförmige Gate-Elektroden gelegt, die ebenfalls parallel ausgerichtet waren. Es ergab sich somit eine gitterförmige Anordnung von Kreuzungspunkten.

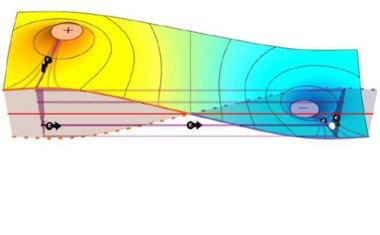

An jedem Kreuzungspunkt eines Nanodrahts mit einer Gate-Linie war ein Feldeffekttransistor entstanden, der in der Zirkonoxidschicht einen zusätzlichen, nichtflüchtigen Ladungsspeicher besaß. Mit Hilfe des Ladungszustands ließ sich die Leitfähigkeit der Nanoröhre zwischen zwei verschiedenen Zuständen hin und her schalten. In der Röhre fand der Ladungstransport durch positive Löcher statt. Wurde zwischen Gate- und Source-Elektrode eine positive Spannung von 8 V angelegt, so verdrängte die positive Gate-Elektrode die positiven Löcher im darunter liegenden Abschnitt des Nanodrahts. Der Löchermangel führte dazu, dass der Draht eine sehr geringe Leitfähigkeit hatte.

In der Zirkonoxidschicht unter der positiven Gate-Elektrode sammelten sich negative Ladungen, die anschließend dort festsaßen. Wurde nun die Gate-Spannung auf 4 V reduziert, so kam die löcherabstoßende Wirkung des Gates nicht mehr gegen die löcheranziehende Wirkung der festsitzenden negativen Ladungen an: Der Nanodraht wurde wieder von Löchern erfüllt und seine Leitfähigkeit erhöhte sich sprunghaft. Verringerte man die Gatespannung auf –8 V, so blieb die Leitfähigkeit des Nanodrahtes hoch, doch die festsitzenden negativen Ladungen wurden verdrängt und durch festsitzende positive Ladungen ersetzt. Die machten sich bemerkbar, als die Gate-Spannung auf 0 V gebracht wurde, da sie nun die positiven Löcher im Nanodraht verdrängten, worauf sich seine Leitfähigkeit sprunghaft verringert.

Der Nanodrahttransistor zeigte somit eine Hysterese: Zwischen 0 V und 4 V gab es zwei Zustände, einen mit hoher und einen mit niedriger Leitfähigkeit. Zwischen diesen „aktiven“ und „passiven“ Zuständen konnte man mit Hilfe der Gate-Spannung hin und her schalten. Die an den einzelnen Gate-Linien liegenden Spannungen waren die Inputs und die an den Nanodrähten liegenden Spannungen, die von den Zuständen der Transistoren abhingen, waren die Outputs. Die Forscher verknüpften nun zwei solcher gitterförmigen Anordnungen von Transistoren zu einem Prozessor, indem sie die Nanodrähte der einen Anordnung mit den Gate-Elektroden der anderen verbanden. Sie „programmierten“ den Prozessor, indem sie die Transistoren mit hinreichend großen Spannungen in die richtigen Zustände brachten. Anschließend ließen sie den Prozessor mit kleineren Spannungen arbeiten. Auf diese Weise konnte er Bits addieren, subtrahieren oder zum Multiplexer oder Demultiplexer werden.

Insgesamt fertigten Lieber und seine Kollegen 496 programmierbare NWFET (Nanowire FET), die auf einer Fläche von 960 µm2 miteinander verschaltet waren. Die Forscher sind indes zuversichtlich, dass man die benötigte Fläche auf etwa 1 µm2 verkleinern kann. Da die einzelnen Transistoren ein Inputsignal verstärken können, könnte man sie in größerer Zahl hintereinander schalten. Darüber hinaus ist das von den Forschern entwickelte Verfahren skalierbar, so dass sich auch aufwendigere Prozessoren herstellen ließen, die kompliziertere Operationen durchführen könnten.

RAINER SCHARF

Weitere Infos

Weitere Literatur:

- W. Lu & C. M. Lieber: Nanoelectronics from the bottom up. Nature Mater. 6, 841 (2007)

dx.doi.org/10.1038/nmat2028

cmliris.harvard.edu/publications/2000s/2007/NatureMater_6_841.pdf (frei!) - Wie Lu et al.: Nanowire transistor performance limits and applications. IEEE Trans. Electron. Dev. 55, 2859 (2008)

dx.doi.org/10.1109/TED.2008.2005158

cmliris.harvard.edu/publications/2000s/2008/IEEETransED_55-2859_Lu.pdf (frei!) - Jie Xiang et al.: Ge/Si nanowire heterostructures as high-performance field-effect transistors. Nature 441, 489 (2006)

dx.doi.org/10.1038/nature04796

cmliris.harvard.edu/publications/2000s/2006/Nature_441_489.pdf (frei!) - A. Javey et al.: Layer-by-Layer Assembly of Nanowires for Three-Dimensional, Multifunctional Electronics. Nano Lett. 7, 773 (2007)

dx.doi.org/10.1021/nl063056l

cmliris.harvard.edu/publications/2000s/2007/NanoLett_7_773.pdf (frei!)

AL