Simulationen für die Nanoelektronik

Neues Projekt beschäftigt sich mit Simulationsverfahren für die Entwicklung neuartiger Transistorstrukturen.

Die Leistung neuer Computerchips verdoppelt sich etwa alle zwei Jahre. Immer mehr Transistoren finden auf einem Mikroprozessor Platz aber die bekannten Herstellungsverfahren stoßen an ihre technischen Grenzen. Neue Verfahren für die Miniaturisierung der Bauteile werden in weltweiten Verbünden von Hochschulen und Industrie entwickelt. Bis zur Produktionsreife einer neuen Generation von Prozessoren sind umfangreiche Vorarbeiten nötig. Hier setzt ein Projekt Arbeitsgruppe Nanoelektronik / Bauelementmodellierung an der TH Mittelhessen an, das sich mit Simulationsverfahren für die Entwicklung neuartiger Transistorstrukturen befasst.

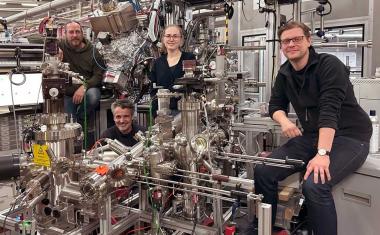

Abb.: Projektbesprechung mit Alexander Klös, Harith Al Khafji, Fabian Hosenfeld und Michael Gräf (von links; Bild: THM).

„Die Simulation der Funktionsweise der Chips muss heute zunehmend die Brücke schlagen zwischen besonderen physikalischen Effekten in Schaltelementen, die nur wenige Nanometer groß sind, hin zu einem Gesamtsystem aus mehreren Milliarden Transistoren“, erläutert Projektleiter Alexander Klös. Hierfür entwickelt die Arbeitsgruppe, die im Kompetenzzentrum Nanotechnik und Photonik der THM angesiedelt ist, neuartige effiziente Simulationsverfahren. Außerdem arbeiten die Wissenschaftler daran, prozesstechnische Schwankungen bei der Herstellung der Mikrochips in die Simulationen einzubeziehen und damit die Ausbeute der Technologie zu erhöhen. Die zukünftigen Transistoren, um die es in dem Projekt geht, sind weniger als zwanzig Nanometer groß.

Das Forschungsvorhaben hat eine Laufzeit von vier Jahren und wird im Rahmen des Programms „IngenieurNachwuchs“ vom BMBF mit 432.000 Euro gefördert. Kooperationspartner sind die Universität Rovira i Virgili im spanischen Tarragona und die Firma Admos Advanced Modeling Solutions in Frickenhausen.

THM / AH