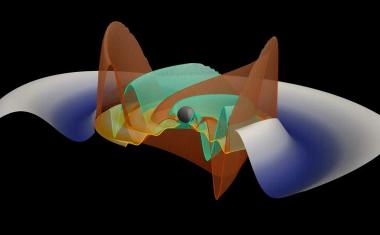

In Silizium-Wafern können schon wenige Versetzungen zu fehlerhaften Computer-Chips und somit zu unerwünschtem Ausschuss in der Produktion führen. „Daher ist es wichtig zu verstehen, wie sich ein minimaler mechanischer Oberflächenfehler unter typischen Prozesseinwirkungen, wie zum Beispiel Hitze, in die Tiefe des Kristalls entwickelt“, sagt Daniel Hänschke vom Karlsruher Institut für Technologie. Sein Team konnte nun Versetzungen präzise vermessen und ihre Wechselwirkung untereinander und mit äußeren Einflüssen untersuchen. Die Analyse zeigt, wie sich von einem einzigen Oberflächendefekt eine ganze Armada von hexagonalen Defektlinien ausbreitet, wobei im Zentrum eines solchen dreidimensionalen Netzes völlig ungestörte Bereiche verbleiben können. „Die auftretende kollektive Bewegung kann auf der gegenüberliegenden Seite des Wafers zu einem Heben oder Senken von beträchtlichen Flächenbereichen führen und störende Stufen bilden, was sich dort dann zum Beispiel nachteilig auf die Fertigung und Funktion von Mikrostrukturen auswirkt“, so Hänschke.

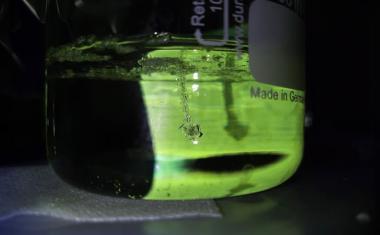

Abb.: Kleine Oberflächenfehler können bei der Verarbeitung von Halbleiter-Wafern zu weitläufige Defekten im Inneren und Stufen in großen Oberflächenarealen führen. (Bild: D. Hänschke, KIT)

In Kombination mit mathematischen Modellrechnungen erlauben es die Ergebnisse, die zugrunde liegenden physikalischen Prinzipien besser zu verstehen. „Bisherige Modelle beruhen vorwiegend auf Daten, die man an sehr kleinen Kristallproben mit Hilfe der Elektronenmikroskopie gewonnen hat“, erläutert Team-Mitglied Elias Hamann. „Mit unserer Methode können wir jedoch auch große, flächige Kristalle untersuchen, wie zum Beispiel handelsübliche Wafer. Nur so können die genauen Zusammenhänge aufgedeckt werden, die zwischen anfänglichen, winzigen Originalschäden und den umfassenden daraus folgenden Kristalldeformationen bestehen, welche dann wiederum weit weg vom Ausgangspunkt zu Problemen führen können.“

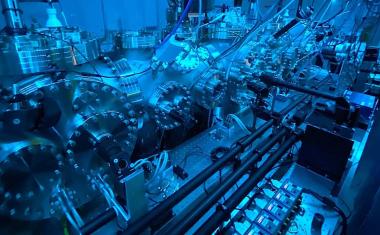

Die neue Messmethode nutzt Röntgenmethoden am Synchrotron KARA des KIT und am Europäischen Synchrotron ESRF in Grenoble, sowie die CDIC-Lichtmikroskopie. Die damit möglichen Erkenntnisse werden die bestehenden Modelle für die Vorhersage von Defektentstehung und -ausbreitung verbessern und damit wichtige Hinweise darauf liefern, wie der Herstellungsprozess von Computer-Chips optimiert werden kann. Schon heute werden pro Quadratzentimeter Oberfläche eines Wafers mehrere Milliarden Transistoren untergebracht – und die Tendenz ist nach wie vor steigend. Schon jetzt führen noch so kleine Fehler auf und im Kristall zum Ausfall Tausender dieser winzigen Schaltungen, was betroffene Chips unbrauchbar machen kann. Die Industrie hat ein großes Interesse daran, diesen Ausschuss auch in Zukunft zu minimieren.

KIT / RK